数字逻辑电路设计| 课程教学大纲书圈2022-08-23 08:00

[size=0.32][url=]+订阅[/url]

“十二五”普通高等教育本科国家级规划教材

江苏省高等学校重点教材

★采用 VHDL描述电路的设计

★每章均附有 小结、习题与思考题

★ 30小时超详细微课视频覆盖全书内容

★配套 PPT课件、教学大纲和实验教材

✦

“数字逻辑”课程教学大纲(72课时)

✦

| [size=0.48]学分 | [size=0.48]4 |

| [size=0.48]学时 | [size=0.48]72(其中,课堂教学56学时,实验16学时) |

| [size=0.48]先修课程 | [size=0.48]大学物理、离散数学 |

| [size=0.48]适用专业 | [size=0.48]计算机类 |

| [size=0.48]教材 | |

| [size=0.48]开课学院 | [size=0.48]计算机科学与通信工程学院 |

1

课程性质与课程目标

(一)课程性质(需说明课程对人才培养方面的贡献)

“数字逻辑”课程是计算机类及相近专业的专业基础课,在学习了大学物理、离散数学基础课程后的一门课程,学生通过本课程的学习,能够掌握数字电路及数字逻辑的基本知识,能够分析和设计基本的数字逻辑电路,了解硬件描述语言(VHDL)、可编程器件(PLD、CPLD、HDPLD、FPGA)、在系统编程技术(ISP)及EDA技术的设计思想等内容,为后续的计算机专业课程打下基础。

(二)课程目标(根据课程特点和对毕业要求的贡献,确定课程目标。应包括知识目标和能力目标)

1. 知识方面

1.1 掌握数字电路的基础知识如数制和编码、逻辑代数等;

1.2 了解门电路、触发器等基本结构及工作原理;

1.3 掌握组合逻辑、时序逻辑的分析和设计的方法;

1.4 掌握硬件描述语言(VHDL)描述逻辑电路的方法;

1.5 了解可编程器件(PLD、CPLD、HDPLD、FPGA)、系统编程技术(ISP)及EDA技术的设计思想等内容。

2. 能力与素质方面

2.1 掌握运用逻辑代数设计逻辑电路的方法;

2.2 具有数字逻辑电路分析与设计的基本能力;

2.3 能够运用VHDL语言编程设计简单的数字逻辑电路;

2.4 具有使用EDA开发工具对FPGA芯片进行开发应用的基本能力;

2.5 逐步培养学生的综合设计能力。

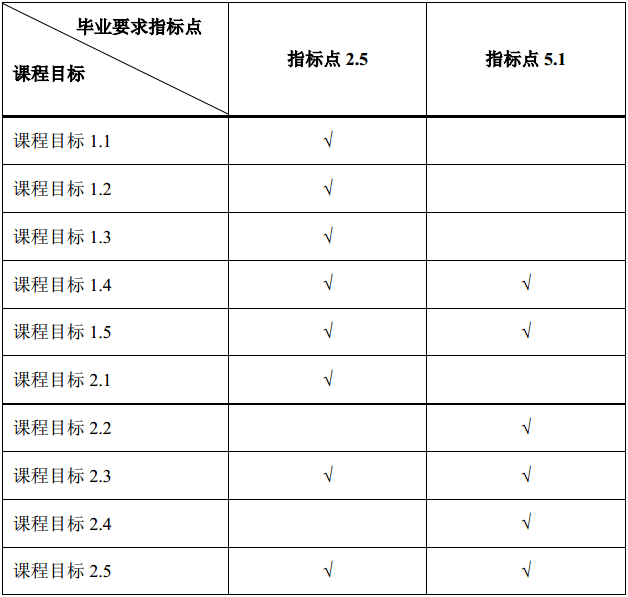

(三)课程目标与专业毕业要求指标点的对应关系(认证专业必修课程填写)

本课程支撑专业培养计划中毕业要求指标点2.5和5.1。

1.毕业要求2.5:具备将工程基础知识、计算机基础知识用于计算机领域复杂工程模型验证求解的能力。

2.毕业要求5.1:了解计算机科学与技术发展现状和趋势。

*注:课程目标与毕业要求指标点对接的单元格中可输入“ ✓”,也可标注“H、M、L”。

2

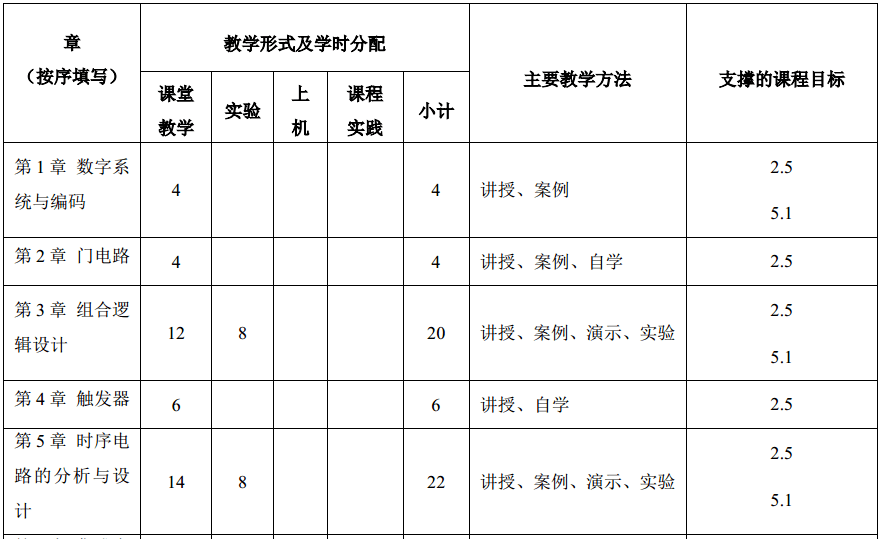

课程内容与教学要求(按章撰写)

第1章 数字系统与编码

【课程内容】

1. 本课程的性质、学习方法、目的、任务。(讲授)

2. 数制及数制之间的转换,原码、反码、补码的概念。(讲授)

3. 十进制数的编码及可靠性编码。(讲授)

【教学要求】

掌握数字系统的进制和编码的基本知识。

【重点与难点】

1.重点

(1)二进制与十进制之间的关系。

(2)带符号数的表示。

2.难点

可靠性编码中的汉明码。

第2章 门电路

【课程内容】

1. 数字信号基础。(讲授)

2. 基本逻辑门电路。(讲授)

3. TTL集成门电路基本结构和工作原理。(讲授)

4. CMOS集成门电路基本结构及工作原理。(讲授)

【教学要求】

1. 掌握门电路的基本知识。

2. 了解TTL与CMOS集成电路的原理与特点。

【重点与难点】

1.重点

(1)与或非门的表示及复合门的表示。

(2)TTL与CMOS集成电路。

2.难点

TTL与CMOS集成电路的工作原理。

第3章 组合逻辑的分析与设计

【课程内容】

1. 逻辑代数基础。(讲授)

2. 逻辑函数的化简。(讲授+案例)

3. 组合逻辑电路的分析。(讲授+案例)

4. 组合逻辑电路的设计。(讲授+案例+实验)

5. VHDL描述基础。(讲授+自学+实验)

6. 组合逻辑电路设计举例。(案例)

7. 组合逻辑电路中的竞争和现象。(讲授+案例)

【教学要求】

1. 掌握逻辑代数的基本知识。

2. 理解运用逻辑代数分析和优化组合逻辑电路。

3. 理解根据需求设计组合逻辑电路。

4. 掌握用VHDL语言描述简单的组合逻辑电路。

【重点与难点】

1.重点

(1)逻辑函数的化简。

(2)组合逻辑电路的VHDL语言描述。

2.难点

逻辑函数的化简和表达式形式变换。

第4章 触发器

【课程内容】

(1) 双稳态触发器的工作原理。(讲授)

(2)单稳触发器、多谐振荡器、施密特触发器。(讲授+自学)

【教学要求】

(1)掌握RS、JK、D、T触发器的基本工作原理和外部逻辑特性。

(2)了解单稳触发器、多谐振荡器、施密特触发器的基本结构及工作原理。

【重点与难点】

1.重点

双稳态触发器的状态表、状态图、次态方程、激励表。

2.难点

RS、JK触发器的逻辑特性。

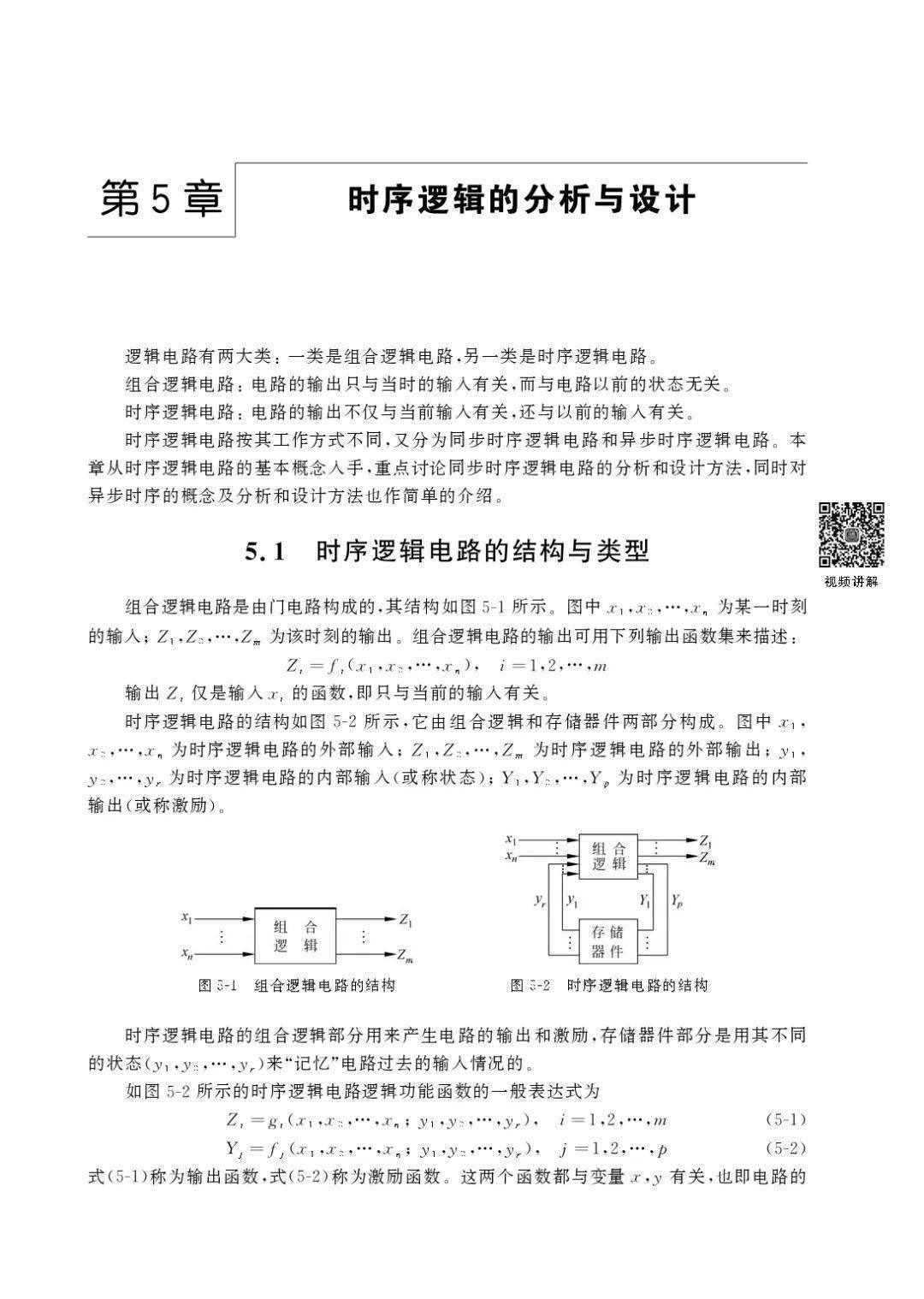

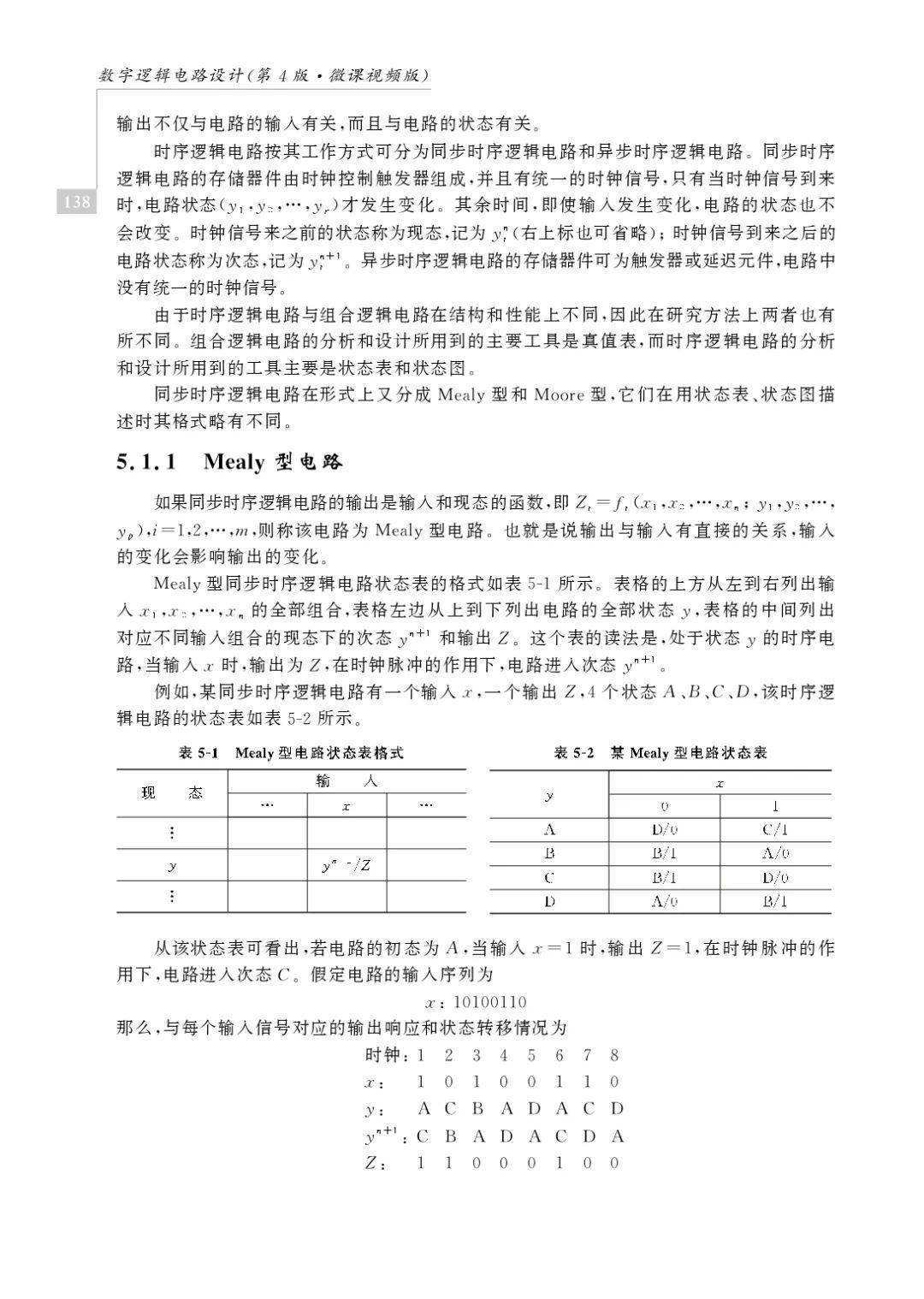

第5章 时序电路的分析与设计

【课程内容】

1. 同步时序逻辑电路的分析。(讲授+案例)

2. 常用同步时序逻辑电路。(讲授+案例)

3. 同步时序逻辑电路的设计。(讲授+案例+实验)

4. VHDL设计时序电路的特点。(讲授+案例+实验)

5. 时序电路设计举例。(讲授+案例+自学)

【教学要求】

1. 掌握时序电路的分析的方法。

2. 理解设计简单的时序电路的方法。

3. 掌握用VHDL语言描述简单的时序逻辑电路。

4. 掌握使用EDA开发环境的方法。

【重点与难点】

1.重点

(1)时序电路的分析与设计。

(2)VHDL语言的时序电路描述。

2.难点

时序电路的设计。

第6章 集成电路的逻辑设计与可编程逻辑器件

【课程内容】

1. 常用中规模通用集成电路设计逻辑电路的方法。(讲授+案例)

2. 半导体存储器基本结构及工作原理。(讲授)

3. 可编程逻辑器件的工作原理。(讲授)

【教学要求】

1. 了解常用中规模通用集成电路。

2. 了解存储器的工作原理。

3. 理解运用现有的集成电路如译码器、多路选择器等设计逻辑电路的方法。

4. 掌握运用可编程器件如ROM、PLA设计逻辑电路。

5. 理解使用EDA开发环境的方法。

【重点与难点】

1.重点

(1)集成电路设计逻辑电路的方法。

(2)可编程逻辑器件。

2.难点

运用现有的集成电路设计逻辑电路。

第7章 高密度可编程器件

【课程内容】

1.ispLSI1016的结构与工作原理。(讲授)

2.在系统可编程原理、器件编程元件的物理布局、 ISP编程接口、ISP

器件的编程方式。(讲授)

3.FPGA的结构与特点。(讲授+自学)

【教学要求】

1. 了解在系统编程技术及相关器件的结构。

2. 了解在系统编程原理。

3. 了解数字电路的发展趋势及EDA技术。

4. 了解FPGA器件的结构与特点。

【重点与难点】

1.重点

(1)在系统编程技术。

(2)ISP与FPGA的特点。

2.难点

FPGA器件的结构与特点。

3

本课程开设的实验项目

实验1 验证全加器和半加器

【实验目的】

(1) 掌握用TTL小规模集成电路设计组成逻辑电路的方法。

(2) 进一步加深对半加器、全加器的逻辑功能的理解。

【实验主要内容】

(1) 根据半加器、全加器的真值表,求出输出函数。

(2) 根据给出的74LS00芯片,将输出函数化成两输入的与非一与非形式。

(3) 在数字系统基本实验单元板上组成实验电路并验证逻辑功能。

【设备要求】

(1) PC机一台;

(2) 安装好Quartus II软件;

(3)数字逻辑实验仪。

实验2 四位加法器的设计

【实验目的】

(1) 了解四位加法器的工作原理。

(2) 掌握基本组合逻辑电路的设计方法。

(3) 熟悉应用Quartus II进行FPGA开发的过程和方法。

(4) 掌握VHDL语言程序的基本结构,初步熟悉VHDL语言设计方法。

【实验主要内容】

(1) 编写四位加法器的VHDL程序,在Quartus II文本输入方式下输入VHDL源程序。

(2) 编译、仿真,锁定管脚、最后下载验证设计。

【设备要求】

(1) PC机一台;

(2) 安装好Quartus II软件;

(3)数字逻辑实验仪。

实验3 七人表决器的设计

【实验目的】

(1) 熟悉VHDL的编程。

(2) 熟悉七人表决器的工作原理。

(3) 进一步熟悉组合电路的设计方法。

【实验主要内容】

(1) 设计一位全加器电路。

(2) 在顶层图中调用全加器和必要的门电路及输入输出连成七人表决电路。

(3) 编译下载,验证功能。

【设备要求】

(1) PC机一台;

(2) 安装好Quartus II软件;

(3)数字逻辑实验仪。

实验4 同步十进制加法计数器74160的实现

【实验目的】

(1) 学会使用VHDL语言设计时序电路。

(2) 用VHDL语言设计74LS160计数器功能模块。

【实验主要内容】

(1) 用VHDL设计一个具有74160功能的电路。

(2) 通过仿真验证结果正确性。

(3) 建立一个名为T74LS160的模块,并以原理图设计方法调用该模块,画出完整的计数器电路。

【设备要求】

(1) PC机一台;

(2) 安装好Quartus II软件;

(3) 数字逻辑实验仪。

实验5 动态扫描电路设计

【实验目的】

(1) 了解数码管的工作原理。

(2) 学习七段数码管显示译码器的设计。

【实验主要内容】

(1) 预习动态数码管显示的相关内容,根据实验内容,写出设计方案。

(2) 使用VHDL语言完成代码的设计。

(3) 使用四个开关作为四位二进制的输入,选择数字信号源模块的时钟频率,下载电路到实验开发系统验证结果。

(4) 理解动态扫描的原理,改变扫描时钟频率会有什么变化,总结动态扫描的频率达到多少时会有稳定的输出。

【设备要求】

(1) PC机一台;

(2) 安装好Quartus II软件;

(3) 数字逻辑实验仪。

实验6 1111序列检测器的设计

【实验目的】

(1) 加深理解序列检测器的工作原理。

(2) 掌握时序电路设计中状态机的VHDL的描述方法。

(3) 进一步掌握用VHDL语言实现复杂时序电路的设计过程。

【实验主要内容】

(1) 根据时序电路设计方法,设计出“1111…”序列检测器电路。

(2) 在图形编辑器窗口中画出电路图。

(3) 编译后通过仿真或下载,验证逻辑功能。

【设备要求】

(1) PC机一台;

(2) 安装好Quartus II软件;

(3) 数字逻辑实验仪。

实验7 简易数字钟的设计

【实验目的】

(1) 了解数字钟的工作原理。

(2) 进一步熟悉用VHDL语言编写驱动七段数码管显示的代码。

(3) 掌握层次化的设计方法。

【实验主要内容】

(1) 录入VHDL源程序实现十进制计数器。

(2) 调用十进制计数器模块,用同步置数方式连成24和60进制计数器。

(3) 调用一个24进制和两个60进制计数器级联构成简易数字钟。

【设备要求】

(1) PC机一台;

(2) 安装好Quartus II软件;

(3) 数字逻辑实验仪。

4

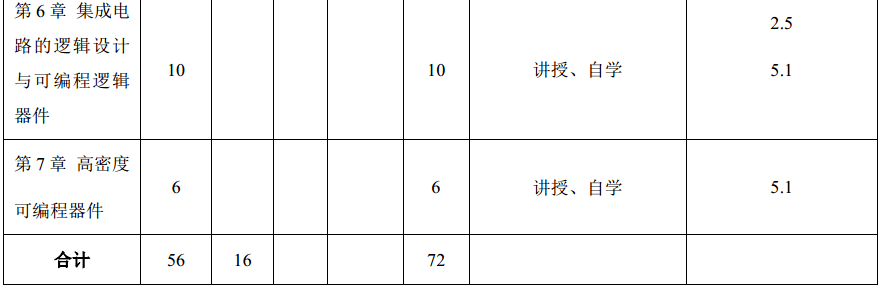

学时分配及教学方法

5

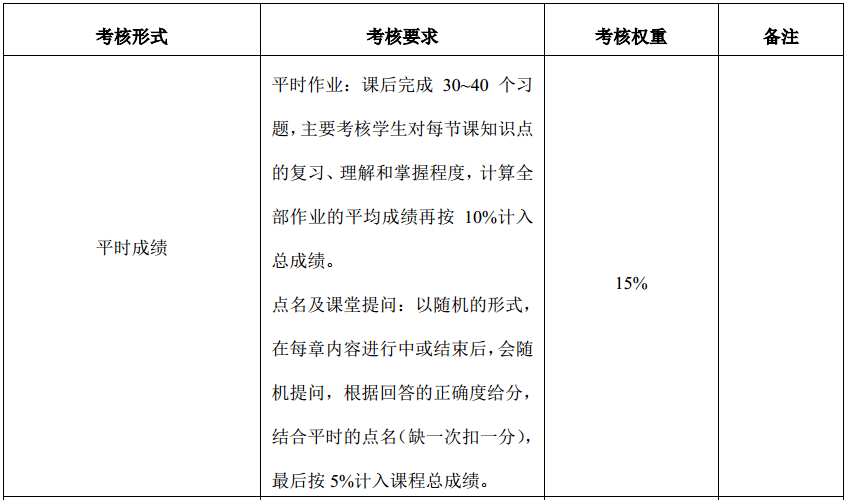

课程考核

6

参考书目及学习资料

1.马汉达、赵念强. 数字逻辑电路设计学习指导与实验教程,清华大学出版社,2015.

2.姜雪松,吴钰淳,王鹰. VHDL设计实例与仿真.北京:机械工业出版社,2007.

3.杨晓慧,杨旭. FPGA系统设计与实例,北京:人民邮电出版社,2010.

4.欧阳星明. 数字逻辑(第三版). 武汉:华中科技大学出版社,2007.

5.阎石. 数字电子技术基础(第4版).北京:高等教育出版社,1998.

7

大纲说明

1.采用多媒体教学。自学可以扫描书中标注的二维码观看微课视频。

2.每次课后布置一些作业,主要是书中所附的习题与思考题。

3.本课程结束后安排1.5周的课程设计,要求见“数字逻辑课程设计”教学大纲。

✦

配套参考教材

✦

《数字逻辑电路设计(第4版·微课视频版)》

作者:鲍可进、赵念强、赵不贿

定价:69.80元

内容简介

本书从数字电路的基础知识出发,介绍数制和编码、门电路、逻辑代数、组合逻辑、触发器、时序逻辑、硬件描述语言(VHDL)、可编程器件(PLD、CPLD、FPGA)、在系统可编程技术(ISP)及EDA技术的设计思想等内容。本书采用VHDL描述电路的设计,每章均附有小结、习题与思考题,大部分内容嵌入了微课视频,并提供全部内容的PPT课件。

本书可作为高等院校计算机、通信、电子信息、自动化等专业“数字逻辑”课程的教材,也可作为相关技术人员的参考书。

目录

向上滑动阅览

第1章数字系统与编码

1.1数字系统中的进位制

1.1.1数制

1.1.2数制转换

1.2数字系统中的编码

1.2.1带符号数的代码表示

1.2.2十进制数的二进制编码

1.2.3可靠性编码

1.2.4字符编码

1.3小结

1.4习题与思考题

第2章门电路

2.1数字信号基础

2.1.1脉冲信号

2.1.2逻辑电平与正、负逻辑

2.2半导体器件的开关特性

2.2.1二极管的开关特性

2.2.2三极管的开关特性

2.2.3MOS管的开关特性

2.3基本逻辑门电路

2.3.1与门、或门和非门

2.3.2复合门

2.3.3三态门与传输门

2.4TTL集成门电路

2.4.1数字集成电路的分类

2.4.2TTL与非门

2.4.3集电极开路的与非门

2.4.4TTL门电路的使用注意事项

2.5CMOS集成门电路

2.5.1CMOS非门

2.5.2CMOS与非门

2.5.3CMOS或非门

2.5.4CMOS三态门

2.5.5CMOS门电路的特点与使用注意事项

2.6TTL电路与CMOS电路之间的接口电路

2.6.1三极管组成的接口电路

2.6.2其他接口电路

2.7小结

2.8习题与思考题

第3章组合逻辑的分析与设计

3.1逻辑代数基础

3.1.1逻辑变量及基本逻辑运算

3.1.2逻辑代数的基本公式、定理与规则

3.1.3逻辑函数及其表达式

3.2逻辑函数的化简

3.2.1代数化简法

3.2.2卡诺图化简法

3.2.3列表化简法

3.2.4逻辑函数化简中的两个实际问题

3.3组合逻辑电路的分析

3.3.1组合逻辑电路分析的一般方法

3.3.2组合逻辑电路分析举例

3.4组合逻辑电路的设计

3.4.1组合逻辑电路设计的一般方法

3.4.2组合逻辑电路设计中应考虑的问题

3.5VHDL描述基础

3.5.1VHDL概述

3.5.2VHDL描述的基本结构

3.5.3VHDL的标识符和保留字

3.6组合逻辑电路设计举例

3.6.1半加器和全加器的设计

3.6.2BCD码编码器和七段显示译码器的设计

3.6.3代码转换器的设计

3.7组合逻辑电路中的竞争与险象

3.7.1竞争与险象的产生

3.7.2险象的分类

3.7.3险象的判断

3.7.4险象的消除

3.8小结

3.9习题与思考题

第4章触发器

4.1双稳态触发器

4.1.1RS触发器

4.1.2JK触发器

4.1.3D触发器

4.1.4T触发器

4.1.5触发器的时间参数

4.2单稳态触发器

4.3多谐振荡器

4.3.1RC环形多谐振荡器

4.3.2石英晶体构成的多谐振荡器

4.4施密特触发器

4.5小结

4.6习题与思考题

第5章时序逻辑的分析与设计

5.1时序逻辑电路的结构与类型

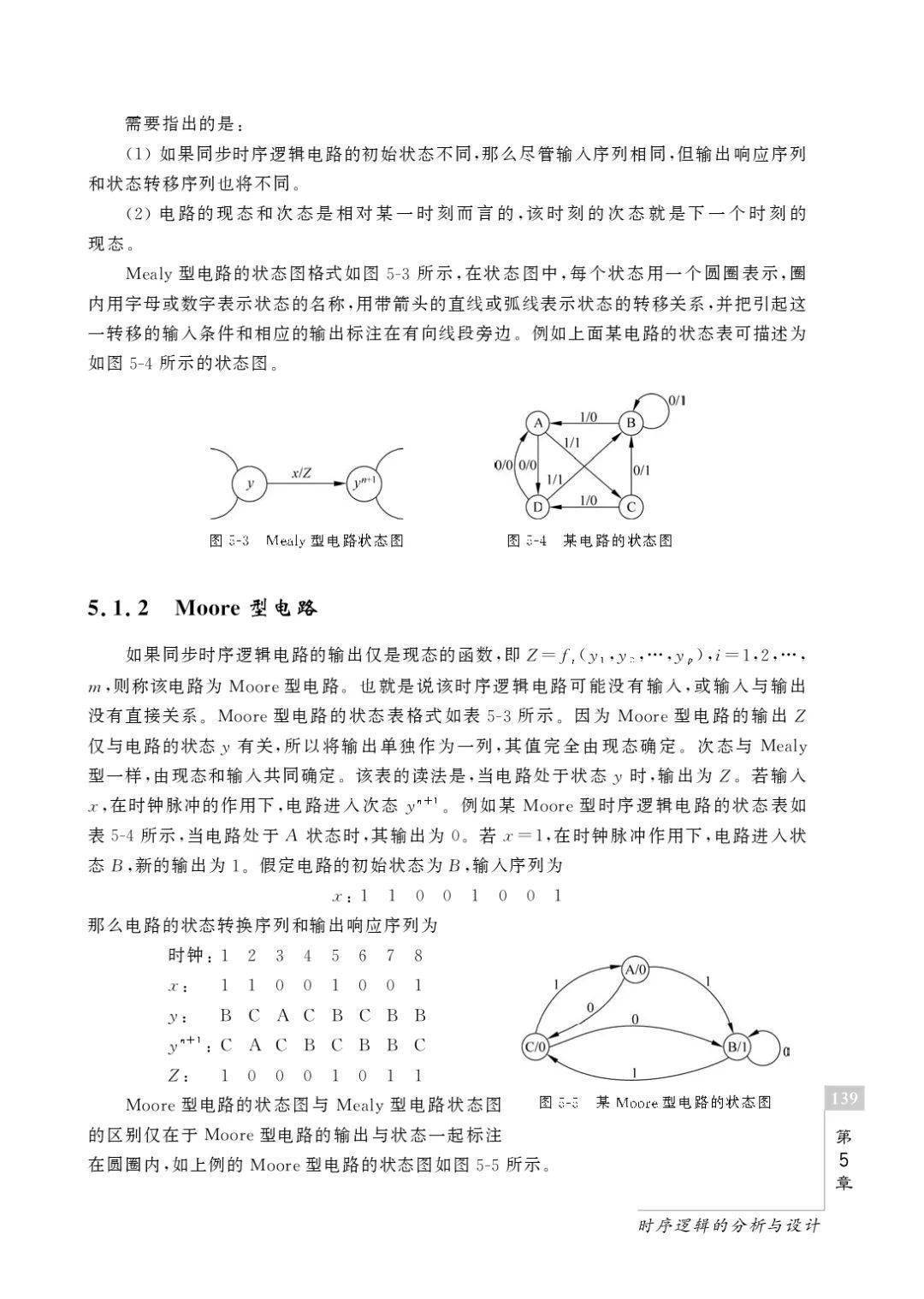

5.1.1Mealy型电路

5.1.2Moore型电路

5.2同步时序逻辑电路的分析

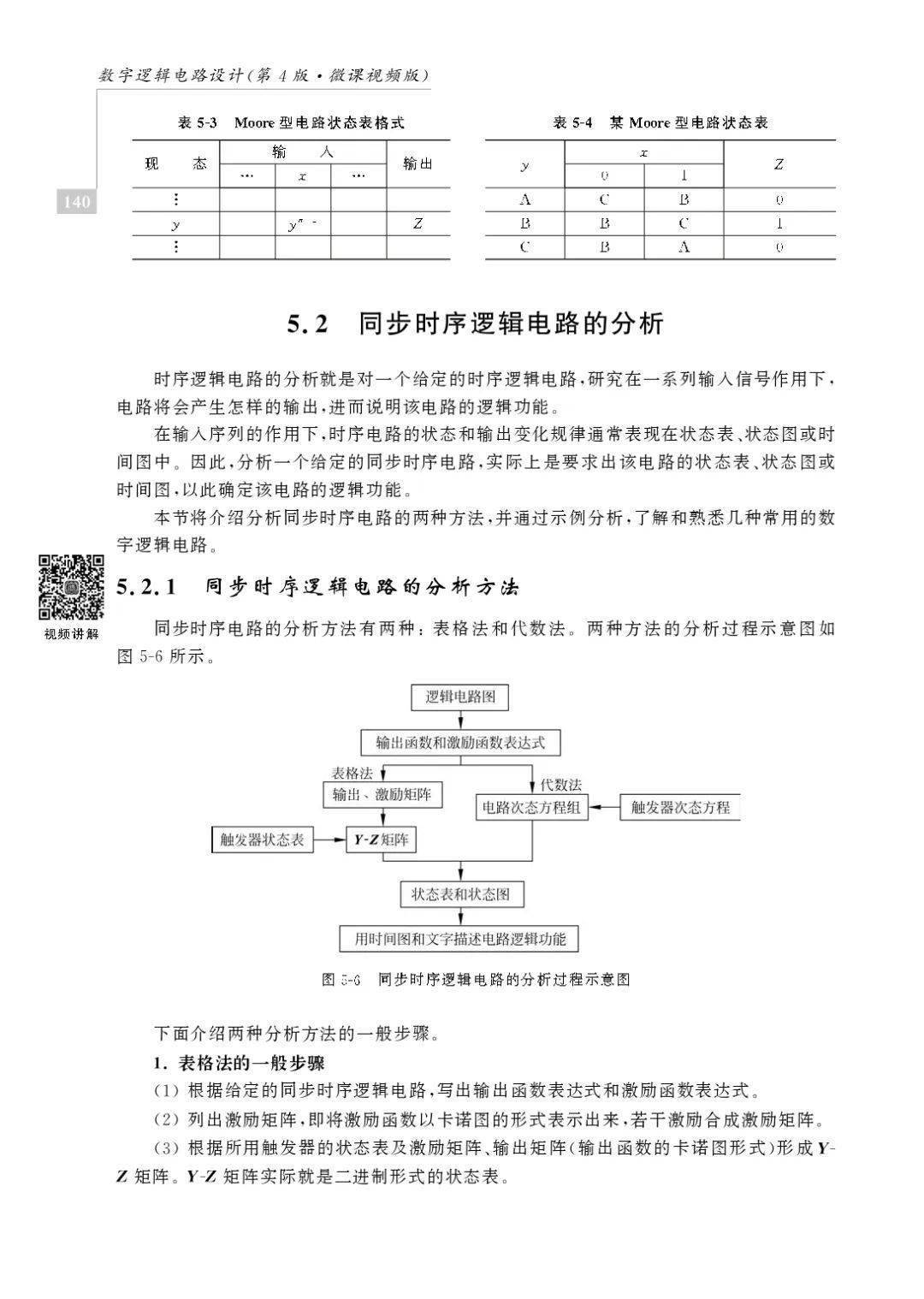

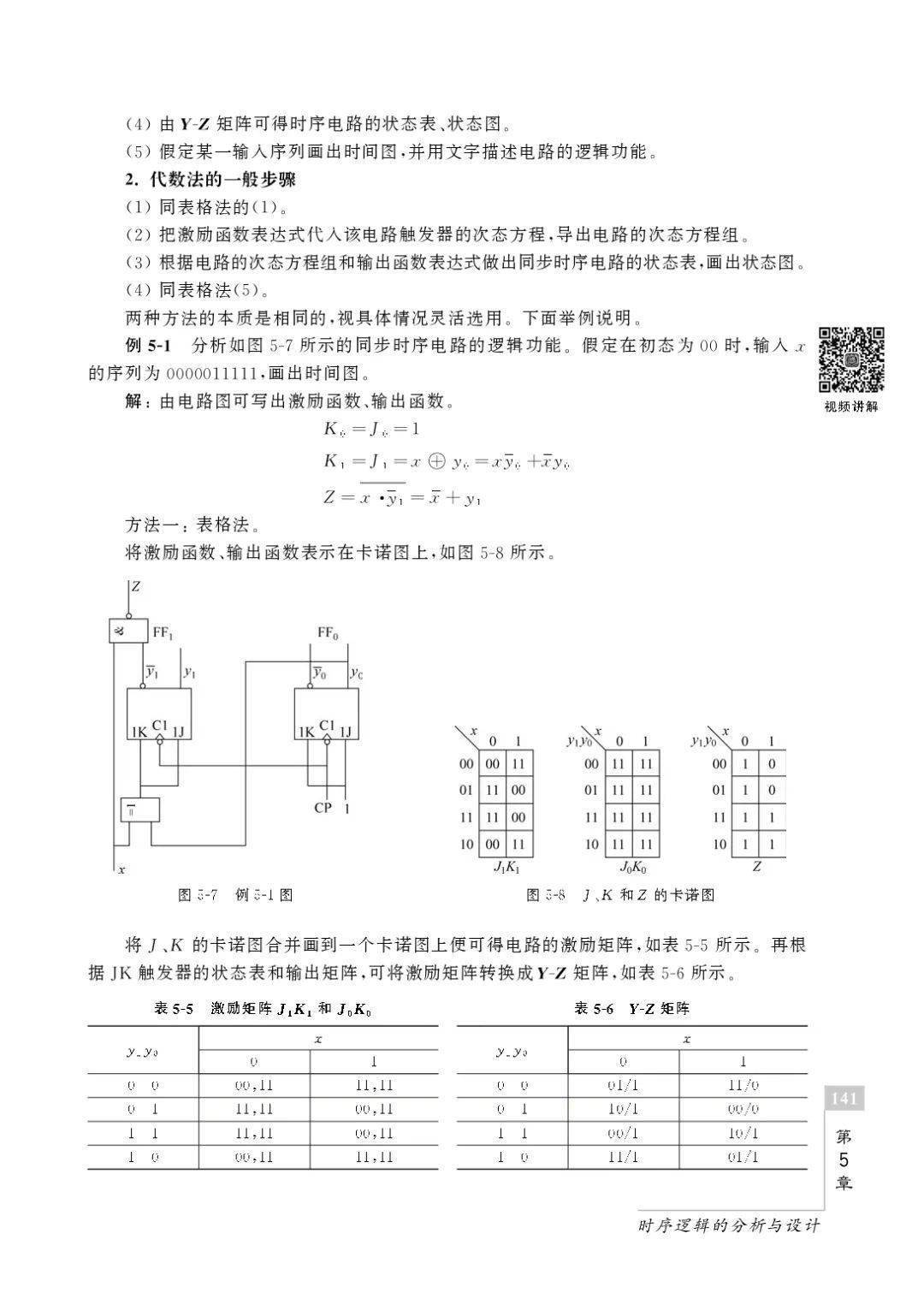

5.2.1同步时序逻辑电路的分析方法

5.2.2常用同步时序逻辑电路

5.3同步时序逻辑电路的设计

5.3.1建立原始状态表

5.3.2状态表的化简

5.3.3状态分配

5.3.4求激励函数和输出函数

5.4VHDL时序电路的设计特点

5.4.1电路的时钟控制

5.4.2状态图的VHDL描述

5.5同步时序逻辑电路设计举例

5.6异步时序逻辑电路

5.6.1脉冲异步时序逻辑电路的分析

5.6.2脉冲异步时序逻辑电路的设计

5.7小结

5.8习题与思考题

第6章集成电路的逻辑设计与可编程逻辑器件

6.1常用中规模通用集成电路

6.1.1二进制并行加法器

6.1.2译码器和编码器

6.1.3多路选择器和多路分配器

6.1.4数值比较器

6.1.5奇偶发生/校验器

6.2半导体存储器

6.2.1概述

6.2.2随机读写存储器

6.2.3只读存储器

6.3可编程逻辑器件

6.3.1PLD概述

6.3.2可编程只读存储器

6.3.3可编程逻辑阵列

6.3.4可编程阵列逻辑

6.3.5通用阵列逻辑

6.4小结

6.5习题与思考题

第7章高密度可编程逻辑器件

7.1在系统可编程技术

7.2ISP器件的结构与原理

7.3在系统编程原理

7.3.1ISP器件编程元件的物理布局

7.3.2ISP编程接口

7.3.3ISP器件的编程方式

7.4FPGA器件

7.4.1FPGA的基本结构

7.4.2FPGA开发流程

7.4.3Altera低成本FPGA

7.4.4Xilinx XC4000系列FPGA

7.4.5XC4000系列FPGA的配置模式

7.5基于可编程逻辑器件的逻辑电路设计实验介绍

7.5.1实验环境

7.5.2基础实验举例

7.5.3多功能数字钟的设计实例

7.6小结

7.7习题与思考题

附录AVHDL基本语句及设计实例

A.1顺序语句

A.2并行语句

A.3属性描述与定义语句

A.4触发器的VHDL描述

A.5CPU基本部件设计举例

参考文献

精彩样章

在公众号书圈后台回复【9787302605751】,下载本书配套的教学资源